- 您现在的位置:买卖IC网 > Sheet目录1214 > EVAL-ADE7878EBZ (Analog Devices Inc)BOARD EVAL FOR ADE7878

�� �

�

�

�ADE7854/ADE7858/ADE7868/ADE7878�

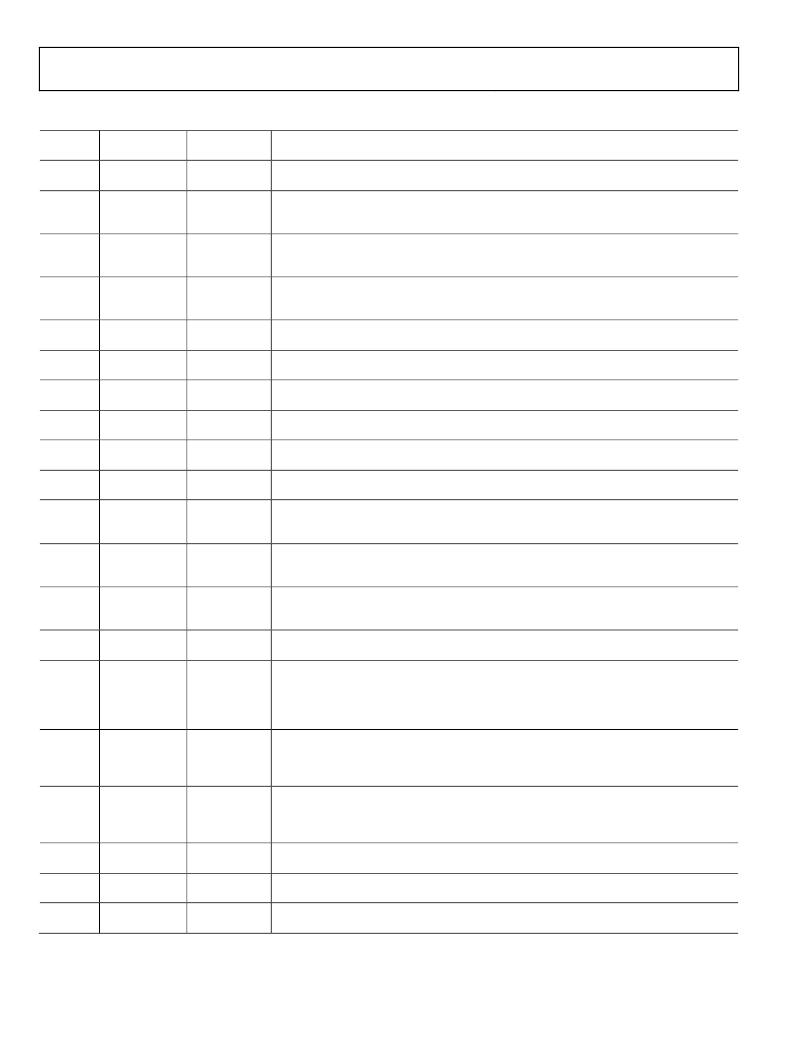

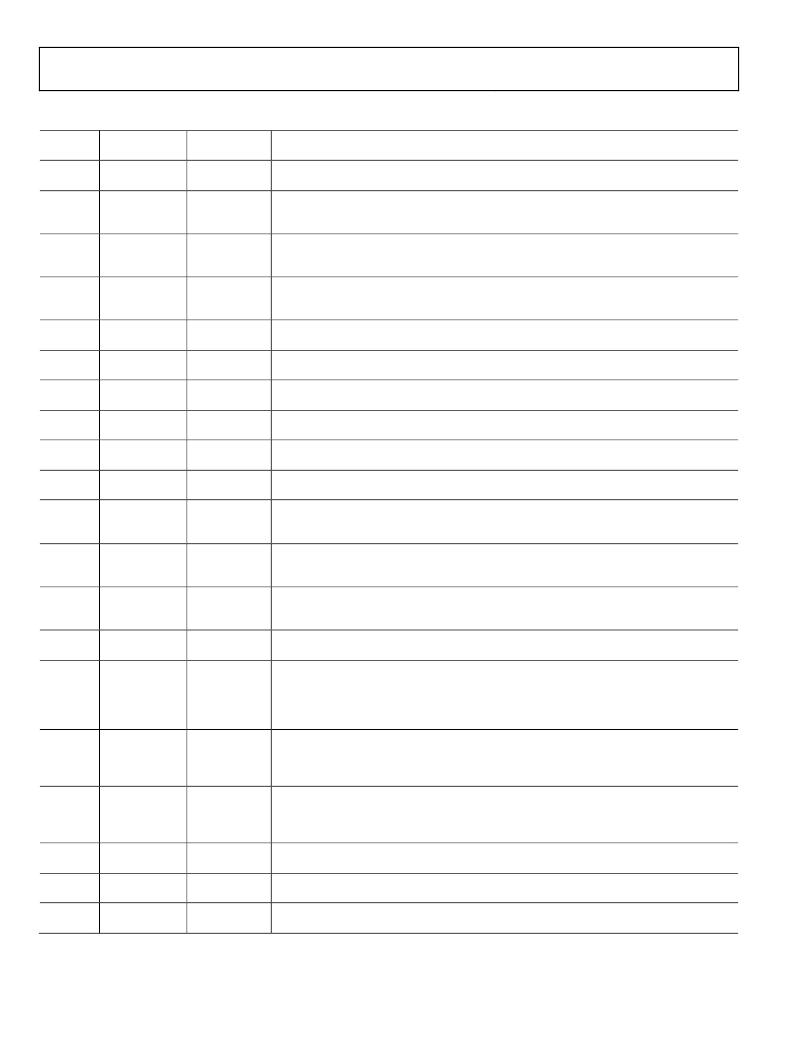

�Table� 39.� MASK0 Register� (Address� 0xE50A)�

�Data� Sheet�

�Bit�

�Location�

�0�

�Bit� Mnemonic�

�AEHF�

�Default� Value�

�0�

�Description�

�When� this� bit� is� set� to� 1,� it� enables� an� interrupt� when� Bit� 30� of� any� one� of� the� total� active�

�energy� registers� (AWATTHR,� BWATTHR,� or� CWATTHR)� changes.�

�1�

�FAEHF�

�0�

�When� this� bit� is� set� to� 1,� it� enables� an� interrupt� when� Bit� 30� of� any� one� of� the� fundamental�

�active� energy� registers� (AFWATTHR,� BFWATTHR,� or� CFWATTHR)� changes.� Setting� this� bit� to1�

��2�

�REHF�

�0�

�When� this� bit� is� set� to� 1,� it� enables� an� interrupt� when� Bit� 30� of� any� one� of� the� total� reactive�

�energy� registers� (AVARHR,� BVARHR,� CVARHR)� changes.� Setting� this� bit� to1� does� not� have� any�

��3�

�FREHF�

�0�

�When� this� bit� is� set� to� 1,� it� enables� an� interrupt� when� Bit� 30� of� any� one� of� the� fundamental�

�reactive� energy� registers� (AFVARHR,� BFVARHR,� or� CFVARHR)� changes.� Setting� this� bit� to1�

��4�

�VAEHF�

�0�

�When� this� bit� is� set� to� 1,� it� enables� an� interrupt� when� Bit� 30� of� any� one� of� the� apparent�

�energy� registers� (AVAHR,� BVAHR,� or� CVAHR)� changes.�

�5�

�LENERGY�

�0�

�When� this� bit� is� set� to� 1,� in� line� energy� accumulation� mode,� it� enables� an� interrupt� at� the� end�

�of� an� integration� over� an� integer� number� of� half� line� cycles� set� in� the� LINECYC� register.�

�6�

�7�

�8�

�9�

�10�

�REVAPA�

�REVAPB�

�REVAPC�

�REVPSUM1�

�REVRPA�

�0�

�0�

�0�

�0�

�0�

�When� this� bit� is� set� to� 1,� it� enables� an� interrupt� when� the� Phase� A� active� power� identified� by�

�Bit� 6� (REVAPSEL)� in� the� ACCMODE� register� (total� or� fundamental)� changes� sign.�

�When� this� bit� is� set� to� 1,� it� enables� an� interrupt� when� the� Phase� B� active� power� identified� by�

�Bit� 6� (REVAPSEL)� in� the� ACCMODE� register� (total� or� fundamental)� changes� sign.�

�When� this� bit� is� set� to� 1,� it� enables� an� interrupt� when� the� Phase� C� active� power� identified� by�

�Bit� 6� (REVAPSEL)� in� the� ACCMODE� register� (total� or� fundamental)� changes� sign.�

�When� this� bit� is� set� to� 1,� it� enables� an� interrupt� when� the� sum� of� all� phase� powers� in� the� CF1�

�datapath� changes� sign.�

�When� this� bit� is� set� to� 1,� it� enables� an� interrupt� when� the� Phase� A� reactive� power� identified�

�by� Bit� 7� (REVRPSEL)� in� the� ACCMODE� register� (total� or� fundamental)� changes� sign.� Setting�

��11�

�REVRPB�

�0�

�When� this� bit� is� set� to� 1,� it� enables� an� interrupt� when� the� Phase� B� reactive� power� identified�

�by� Bit� 7� (REVRPSEL)� in� the� ACCMODE� register� (total� or� fundamental)� changes� sign.� Setting�

��12�

�REVRPC�

�0�

�When� this� bit� is� set� to� 1,� it� enables� an� interrupt� when� the� Phase� C� reactive� power� identified�

�by� Bit� 7� (REVRPSEL)� in� the� ACCMODE� register� (total� or� fundamental)� changes� sign.� Setting�

��13�

�14�

�REVPSUM2�

�CF1�

�0�

�When� this� bit� is� set� to� 1,� it� enables� an� interrupt� when� the� sum� of� all� phase� powers� in� the� CF2�

�datapath� changes� sign.�

�When� this� bit� is� set� to� 1,� it� enables� an� interrupt� when� a� high-to-low� transition� occurs� at� the�

�CF1� pin,� that� is,� an� active� low� pulse� is� generated.� The� interrupt� can� be� enabled� even� if� the�

�CF1� output� is� disabled� by� setting� Bit� 9� (CF1DIS)� to� 1� in� the� CFMODE� register.� The� type� of�

�power� used� at� the� CF1� pin� is� determined� by� Bits[2:0]� (CF1SEL[2:0])� in� the� CFMODE� register�

��15�

�16�

�CF2�

�CF3�

�When� this� bit� is� set� to� 1,� it� enables� an� interrupt� when� a� high-to-low� transition� occurs� at� CF2�

�pin,� that� is,� an� active� low� pulse� is� generated.� The� interrupt� may� be� enabled� even� if� the� CF2�

�output� is� disabled� by� setting� Bit� 10� (CF2DIS)� to� 1� in� the� CFMODE� register.� The� type� of� power�

�used at the CF2 pin is determined by Bits[5:3] (CF2SEL[2:0]) in the CFMODE register (see� Table 45).�

�When� this� bit� is� set� to� 1,� it� enables� an� interrupt� when� a� high� to� low� transition� occurs� at� CF3�

�pin,� that� is,� an� active� low� pulse� is� generated.� The� interrupt� may� be� enabled� even� if� the� CF3�

�output� is� disabled� by� setting� Bit� 11� (CF3DIS)� to� 1� in� the� CFMODE� register.� The� type� of� power�

�used at the CF3 pin is determined by Bits[8:6] (CF3SEL[2:0]) in the CFMODE register (see� Table 45).�

�17�

�DREADY�

�0�

�When� this� bit� is� set� to� 1,� it� enables� an� interrupt� when� all� periodical� (at� 8� kHz� rate)� DSP�

�computations� finish.�

�18�

�REVPSUM3�

�0�

�When� this� bit� is� set� to� 1,� it� enables� an� interrupt� when� the� sum� of� all� phase� powers� in� the� CF3�

�datapath� changes� sign.�

�31:19�

�Reserved�

�00� 0000� 0000�

�Reserved.� These� bits� do� not� manage� any� functionality.�

�0000�

�Rev.� H|� Page� 88� of� 100�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

EVAL-ADE7880EBZ

BOARD EVAL FOR ADE7880

EVAL-ADE7953EBZ

BOARD EVAL FOR ADE7953

EVAL-ADF4002EBZ1

BOARD EVAL FOR ADF4002

EVAL-ADG788EBZ

BOARD EVALUATION FOR ADG788

EVAL-ADM1021AEB

BOARD EVAL FOR ADM1021

EVAL-ADM1023EB

BOARD EVAL FOR ADM1023

EVAL-ADM1031EB

BOARD EVAL FOR ADM1031

EVAL-ADM1062TQEBZ

BOARD EVALUATION FOR ADM1062TQ

相关代理商/技术参数

EVAL-ADE7880EBZ

功能描述:BOARD EVAL FOR ADE7880 RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:* 产品培训模块:Obsolescence Mitigation Program 标准包装:1 系列:- 主要目的:电源管理,电池充电器 嵌入式:否 已用 IC / 零件:MAX8903A 主要属性:1 芯锂离子电池 次要属性:状态 LED 已供物品:板

EVAL-ADE7880EBZ

制造商:Analog Devices 功能描述:ADE7880, ENERGY METER, 3 PH, SPI, I2C, E

EVAL-ADE7913EBZ

制造商:AD 制造商全称:Analog Devices 功能描述:3-Channel, Isolated, Sigma-Delta ADC with SPI

EVAL-ADE7953EBZ

功能描述:BOARD EVAL FOR ADE7953 RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:- 标准包装:1 系列:PSoC® 主要目的:电源管理,热管理 嵌入式:- 已用 IC / 零件:- 主要属性:- 次要属性:- 已供物品:板,CD,电源

EVAL-ADF4001EBZ2

制造商:Analog Devices 功能描述:Evaluation Board For Pll Frequency Synthesizer 制造商:Analog Devices 功能描述:ADF4001 PLL SYNTHESIZER EVAL BOARD

EVAL-ADF4002EB1

制造商:Analog Devices 功能描述:EVAL BOARD - Bulk

EVAL-ADF4002EBZ1

功能描述:BOARD EVAL FOR ADF4002 RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:- 产品培训模块:Obsolescence Mitigation Program 标准包装:1 系列:- 主要目的:电源管理,电池充电器 嵌入式:否 已用 IC / 零件:MAX8903A 主要属性:1 芯锂离子电池 次要属性:状态 LED 已供物品:板

EVAL-ADF4007EBZ1

功能描述:BOARD EVALUATION FOR ADF4007EB1 RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:- 标准包装:1 系列:PSoC® 主要目的:电源管理,热管理 嵌入式:- 已用 IC / 零件:- 主要属性:- 次要属性:- 已供物品:板,CD,电源